**STAM Center**

SECURE, TRUSTED, AND ASSURED MICROELECTRONICS

**ASU** Arizona State University **Engineering**

**CSE 520**

**Computer Architecture II**

Processor Pipelining

Prof. Michel A. Kinsky

1

---

---

---

---

---

---

**STAM Center**

SECURE, TRUSTED, AND ASSURED MICROELECTRONICS

**ASU** Arizona State University **Engineering**

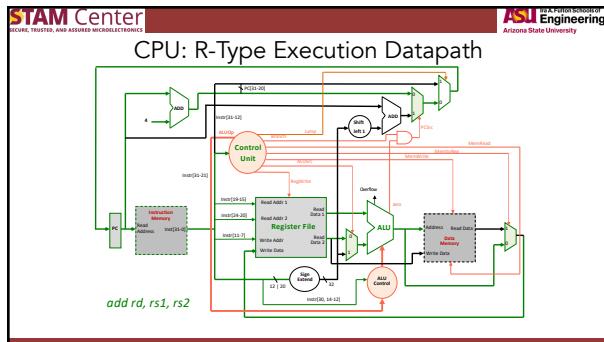

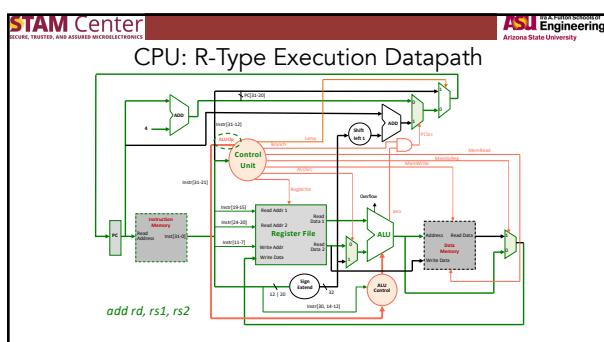

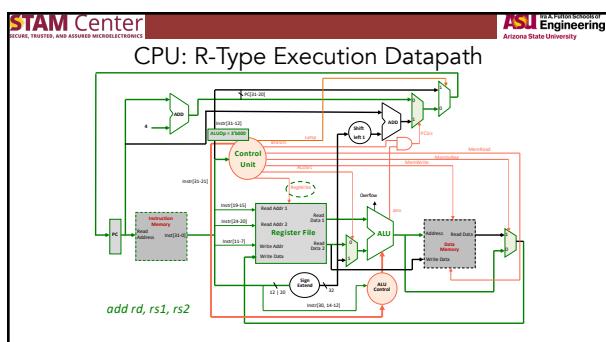

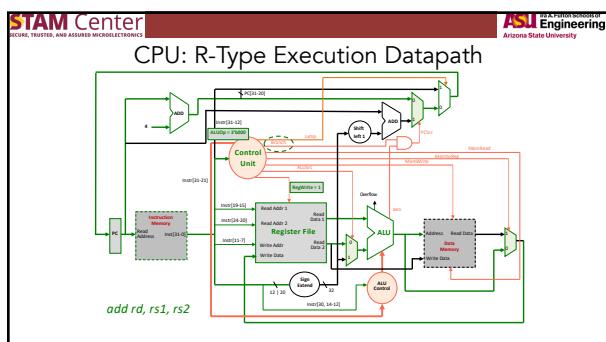

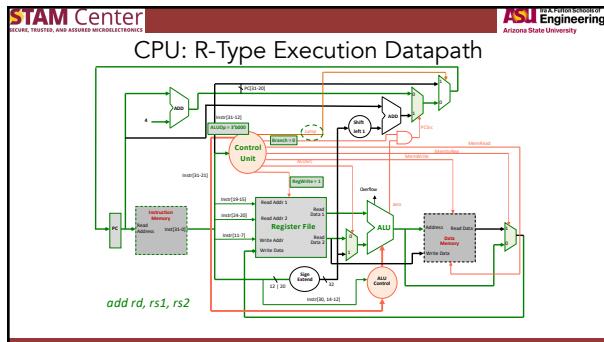

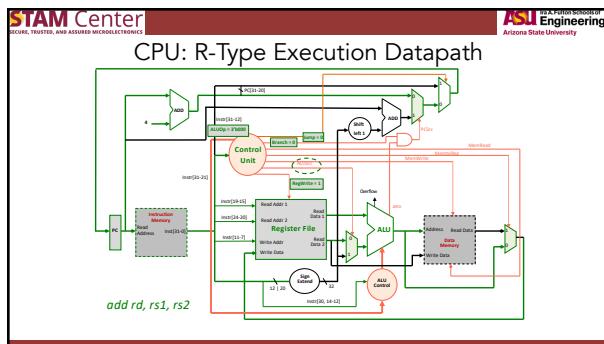

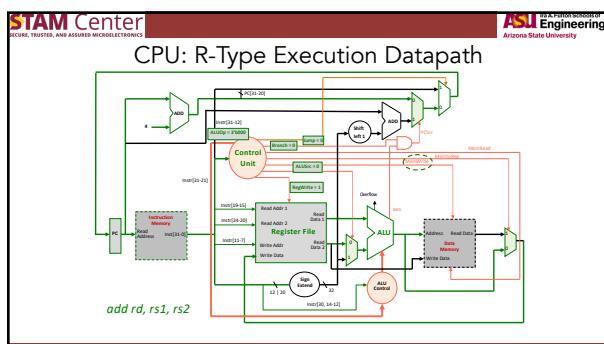

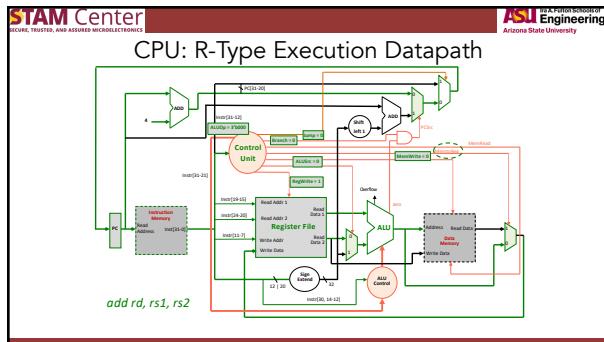

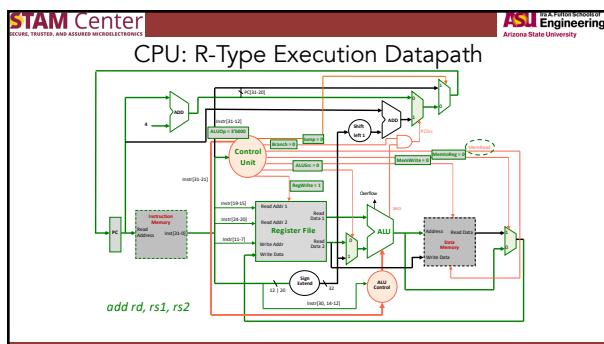

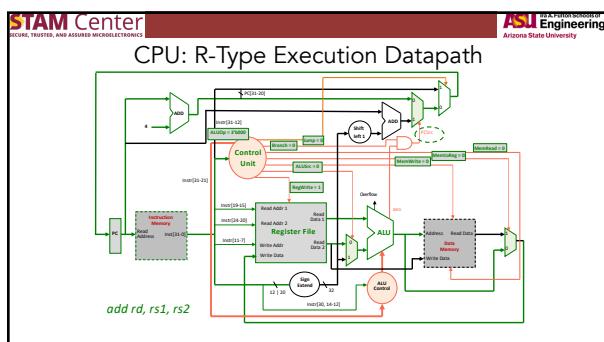

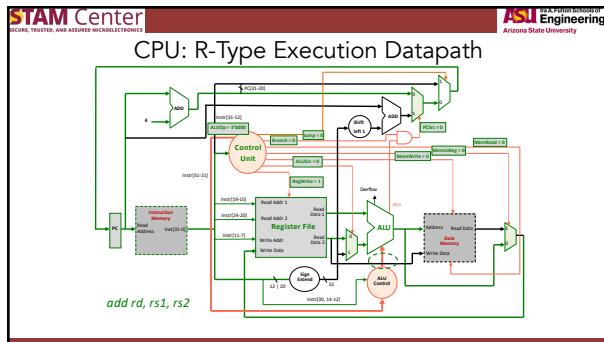

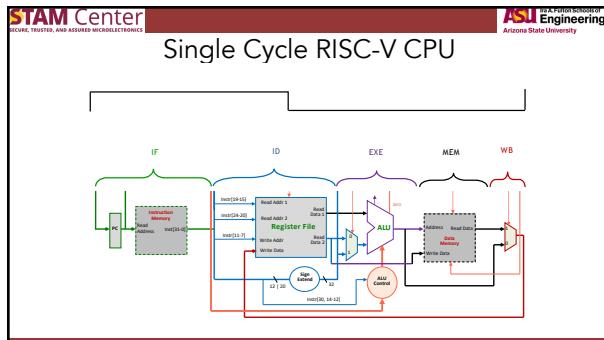

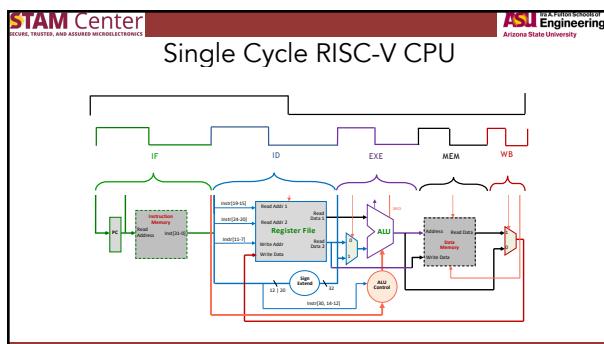

**Central Processing Unit (CPU)**

- Central Processing Unit (CPU) Organization

- CPU Execution Process

- Fetch Instruction

- Decode Instruction

- Execute Operation

- Memory Operation

- Register Writeback Operation

```

graph TD

A[Fetch Instruction] --> B[Decode

Increment PC

Read registers]

B --> C[ALU Operation

Or

Branch Address]

C --> D[Data Memory

Operation]

D --> E[Write Back]

```

2

---

---

---

---

---

---

**STAM Center**

SECURE, TRUSTED, AND ASSURED MICROELECTRONICS

**ASU** Arizona State University **Engineering**

**CPU Control**

| Signal name | Effect when de-asserted                                              | Effect when asserted                                                              |

|-------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| RegDst      | The destination register number comes from <i>rs2</i>                | The destination register number comes from <i>rd</i>                              |

| RegWrite    | None                                                                 | Destination register is written with value on <i>Write data</i>                   |

| ALUSrc      | 2 <sup>nd</sup> ALU operand comes from <i>Read Data 2</i>            | 2 <sup>nd</sup> ALU operand is the sign extended, of some bits of the instruction |

| PCSrc       | The <i>PC</i> is replaced by <i>PC + 4</i>                           | The <i>PC</i> is replaced by the branch target address                            |

| MemRead     | None                                                                 | Memory is read                                                                    |

| MemWrite    | None                                                                 | Memory is written                                                                 |

| MemtoReg    | The value to the register <i>Write data</i> input comes from the ALU | The value to the register <i>Write data</i> input comes from the data memory      |

3

---

---

---

---

---

---

4

---

---

---

---

---

---

---

---

5

---

---

---

---

---

---

---

---

6

---

---

---

---

---

---

---

---

**STAM Center** SECURE, TRUSTED, AND ASSURED MICROELECTRONICS **ASU** Arizona State University **Engineering**

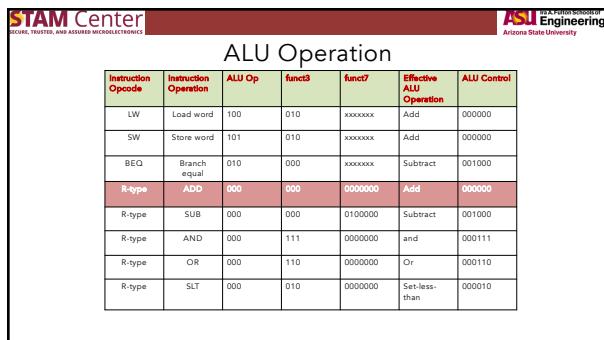

**ALU Operation**

| Instruction Opcode | Instruction Operation | ALU Op | funct3 | funct7  | Effective ALU Operation | ALU Control |

|--------------------|-----------------------|--------|--------|---------|-------------------------|-------------|

| LW                 | Load word             | 100    | 010    | xxxxxx  | Add                     | 000000      |

| SW                 | Store word            | 101    | 010    | xxxxxx  | Add                     | 000000      |

| BEQ                | Branch equal          | 010    | 000    | xxxxxx  | Subtract                | 001000      |

| R-type             | ADD                   | 000    | 000    | 0000000 | Add                     | 000000      |

| R-type             | SUB                   | 000    | 000    | 0100000 | Subtract                | 001000      |

| R-type             | AND                   | 000    | 111    | 0000000 | and                     | 000111      |

| R-type             | OR                    | 000    | 110    | 0000000 | Or                      | 000110      |

| R-type             | SLT                   | 000    | 010    | 0000000 | Set-less-than           | 000010      |

7

---

---

---

---

---

---

---

---

8

---

---

---

---

---

---

---

---

9

---

---

---

---

---

---

---

---

10

---

---

---

---

---

---

---

---

---

---

---

---

11

---

---

---

---

---

---

---

---

---

---

---

---

---

12

---

---

---

---

---

---

---

---

---

---

---

---

---

13

14

15

16

17

18

19

---

---

---

---

---

---

---

---

20

---

---

---

---

---

---

---

---

21

---

---

---

---

---

---

---

---

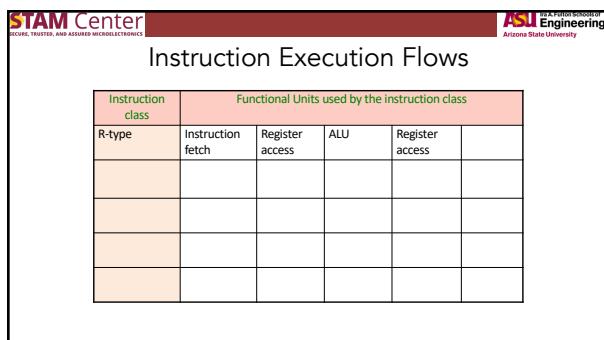

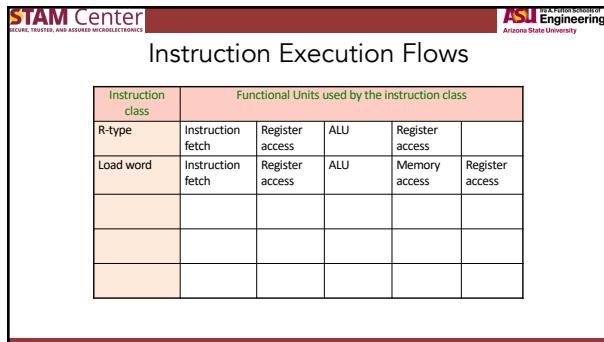

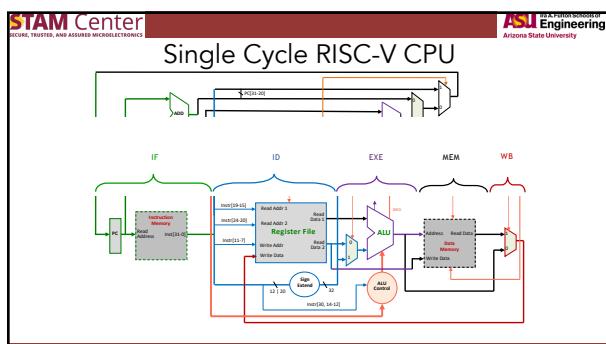

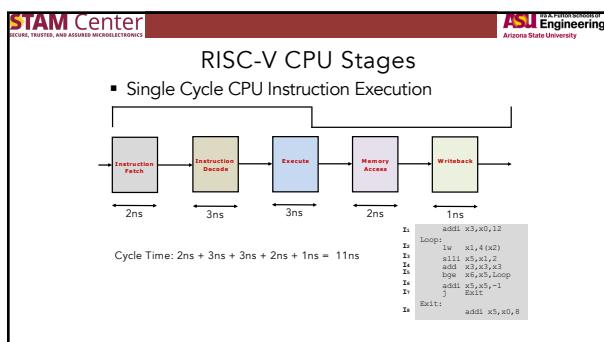

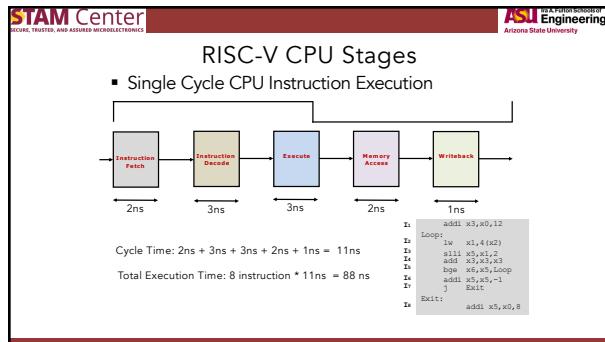

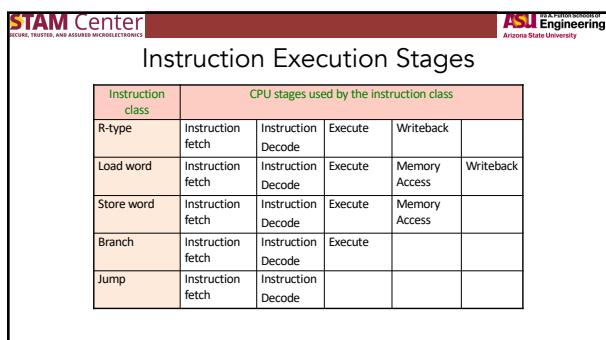

| Instruction Execution Flows |                   | Functional Units used by the instruction class |     |                 |                 |

|-----------------------------|-------------------|------------------------------------------------|-----|-----------------|-----------------|

| Instruction class           |                   | Register access                                | ALU | Register access |                 |

| R-type                      | Instruction fetch | Register access                                | ALU | Register access |                 |

| Load word                   | Instruction fetch | Register access                                | ALU | Memory access   | Register access |

| Store word                  | Instruction fetch | Register access                                | ALU | Memory access   |                 |

| Branch                      | Instruction fetch | Register access                                | ALU |                 |                 |

| Jump                        | Instruction fetch |                                                |     |                 |                 |

22

# CPU Control

23

The diagram illustrates the organization and execution process of a Central Processing Unit (CPU). It is divided into two main sections: 'Central Processing Unit (CPU)' and 'CPU Execution Process'.

**Central Processing Unit (CPU)**

**CPU Execution Process**

- Fetch Instruction

- Decode Instruction

- Increment PC

- Read registers

- ALU Operation

- Or

- Branch Address

- Data Memory Operation

- Write Back

The execution process is shown as a vertical sequence of steps: Fetch Instruction, Decode Instruction, Increment PC, Read registers, ALU Operation, Or, Branch Address, Data Memory Operation, and Write Back. The first four steps are grouped together under the 'Fetch Instruction' box, and the last five steps are grouped together under the 'Decode Instruction' box. The 'ALU Operation' and 'Or' steps are connected by a horizontal line, indicating they are part of the same operation. The 'Branch Address' step follows the 'Or' step. The 'Data Memory Operation' and 'Write Back' steps are connected by a horizontal line, indicating they are part of the same operation.

24

25

26

27

28

---

---

---

---

---

---

29

---

---

---

---

---

---

30

---

---

---

---

---

---

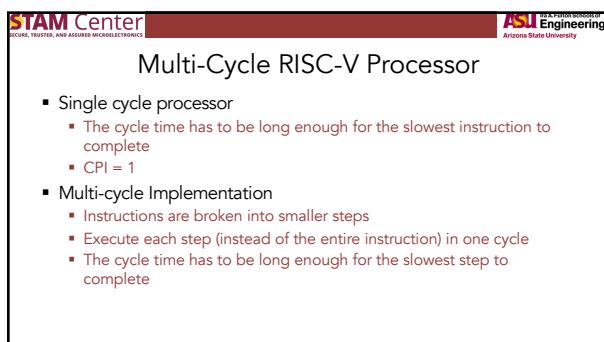

**STAM Center** SECURE, TRUSTED, AND ASSURED MICROELECTRONICS **ASU** Arizona State University **Engineering**

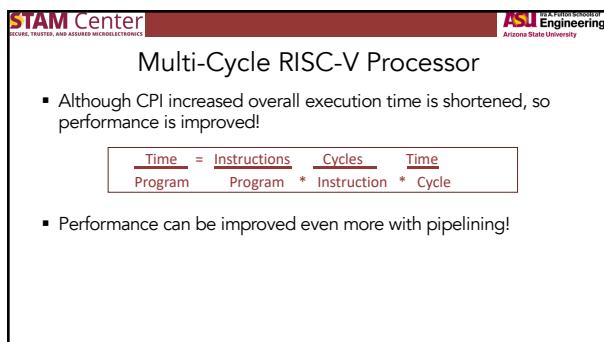

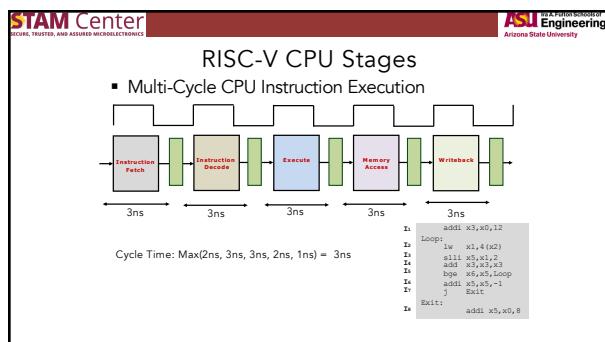

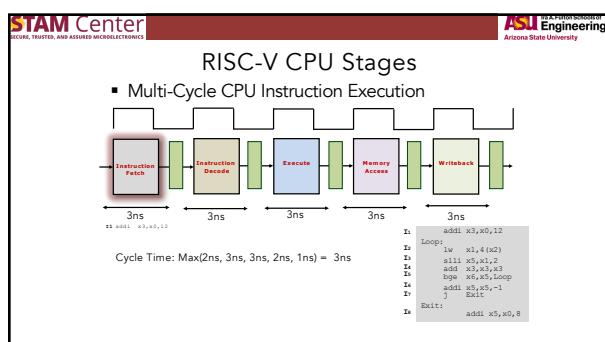

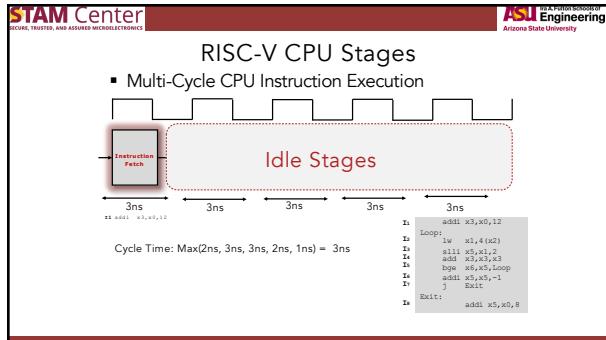

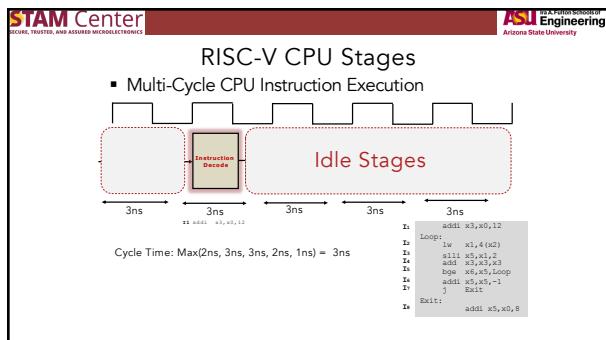

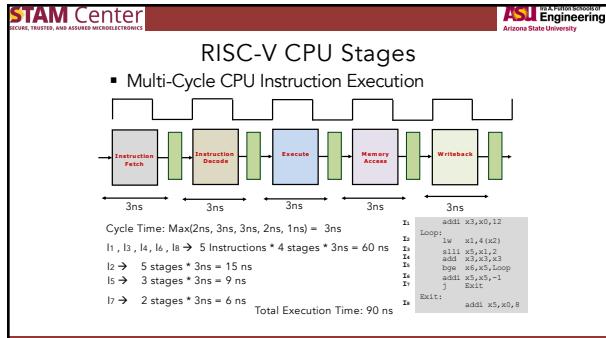

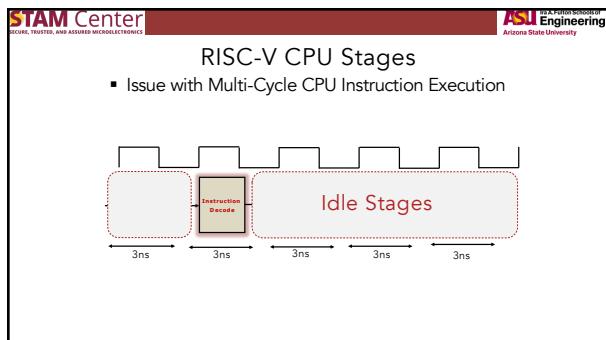

### Multi-Cycle RISC-V Processor

- The advantages of the multiple cycle processor

- Cycle time is much shorter

- Different instructions take different number of cycles to complete

- Load takes five cycles

- Jump only takes three cycles

- CPI is between 3 and 5

```

addi x10, x10, 413

beq x11, x10, label

```

---

---

---

---

---

---

---

31

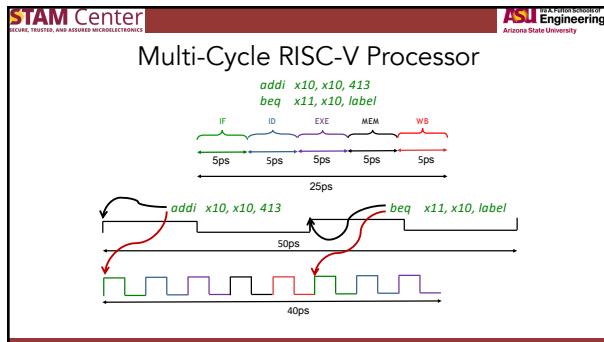

**STAM Center** SECURE, TRUSTED, AND ASSURED MICROELECTRONICS **ASU** Arizona State University **Engineering**

### Multi-Cycle RISC-V Processor

```

addi x10, x10, 413

beq x11, x10, label

```

---

---

---

---

---

---

---

32

**STAM Center** SECURE, TRUSTED, AND ASSURED MICROELECTRONICS **ASU** Arizona State University **Engineering**

### Multi-Cycle RISC-V Processor

```

addi x10, x10, 413

beq x11, x10, label

```

---

---

---

---

---

---

---

33

34

35

36

37

---

---

---

---

---

---

---

---

38

---

---

---

---

---

---

---

---

39

---

---

---

---

---

---

---

---

40

---

---

---

---

---

---

---

---

41

---

---

---

---

---

---

---

---

42

---

---

---

---

---

---

---

---

43

---

---

---

---

---

---

---

---

---

---

44

---

---

---

---

---

---

---

---

---

---

45

---

---

---

---

---

---

---

---

---

---

46

---

---

---

---

---

47

---

---

---

---

---

48

---

---

---

---

---

**STAM Center**

SECURE, TRUSTED, AND ASSURED MICROELECTRONICS

**ASU** Arizona State University

Engineering

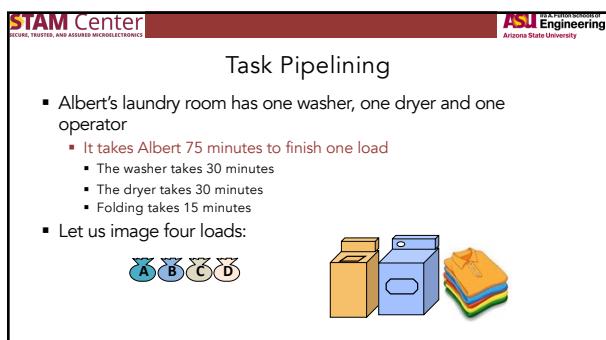

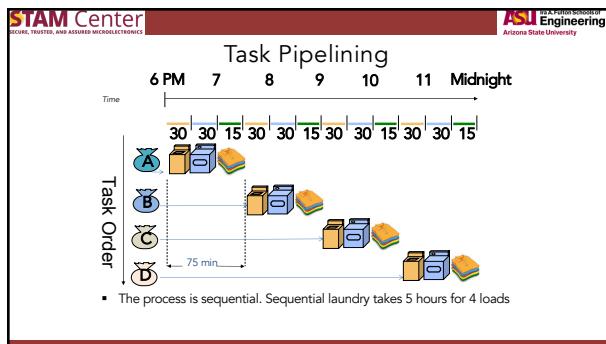

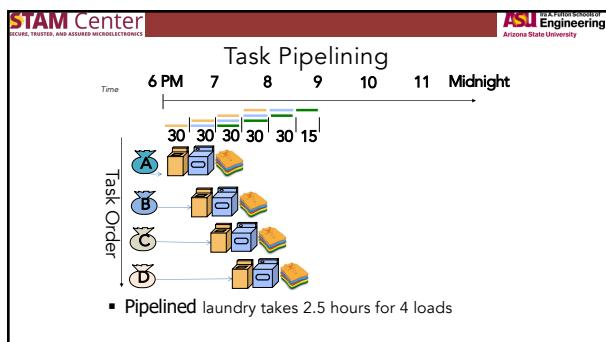

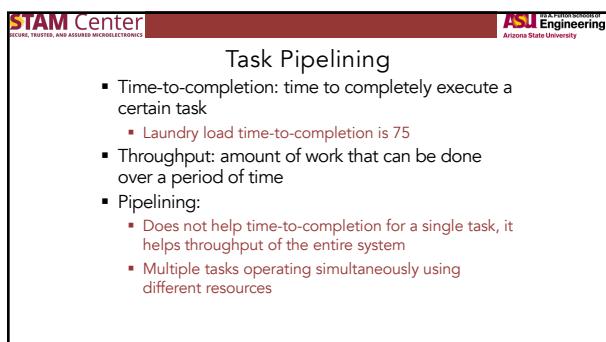

### Task Pipelining

- Time-to-completion: time to completely execute a certain task

- Laundry load time-to-completion is 75

- Throughput: amount of work that can be done over a period of time

- Pipelining:

- Potential speedup related to number of stages

- Time to "fill" pipeline and time to "drain" it reduces speedup

---

---

---

---

---

---

---

49

**STAM Center**

SECURE, TRUSTED, AND ASSURED MICROELECTRONICS

**ASU** Arizona State University

Engineering

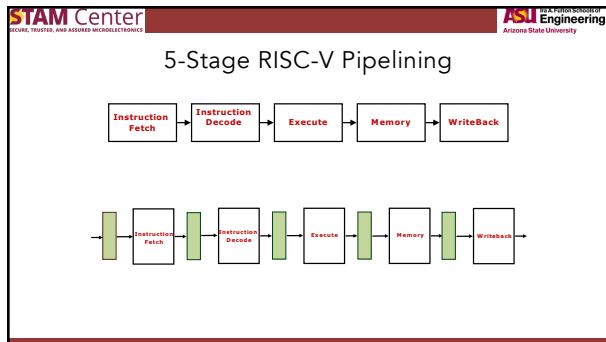

### Task Pipelining

- How to move from stage to stage?

- Buffers/ Registers

---

---

---

---

---

---

---

50

**STAM Center**

SECURE, TRUSTED, AND ASSURED MICROELECTRONICS

**ASU** Arizona State University

Engineering

### Ideal Pipeline

- All objects go through the same stages

- No sharing of resources between any two stages

- Propagation delay through all pipeline stages is equal

---

---

---

---

---

---

---

51

52

---

---

---

---

---

53

---

---

---

---

---