## **STAM** Center

### RTL Design Tools

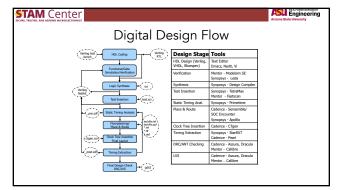

- In this class, we will learn the principles of RTL (register level transfer) coding for synthesis tools through the Verilog hardware description language (HDL) for the design and documentation of out electronic systems.

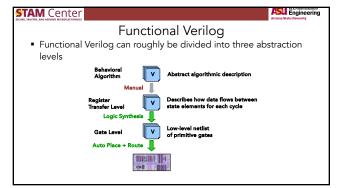

- Verilog allows designers to design at various levels of abstraction.

It is the most widely used HDL

7

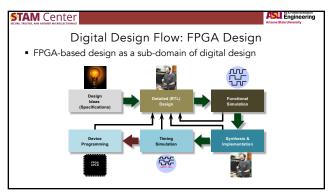

## **STAM** Center ASU Engineering Programmable Logics • Field Programmable Gate Arrays (more on it later) Each cell in array contains a programmable logic function

8

## **STAM** Center ASU Engineering Programmable Logics • Field Programmable Gate Arrays (more on it later) • Array has programmable interconnect between logic functions

| STAM Center                                             | Engineering Arizona State University |

|---------------------------------------------------------|--------------------------------------|

| Verilog Fundamentals                                    |                                      |

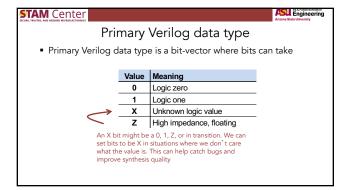

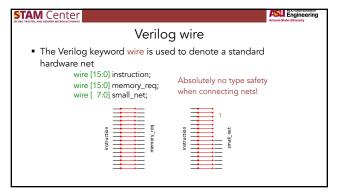

| ■ Data types                                            |                                      |

| <ul><li>Structural Verilog</li></ul>                    |                                      |

| <ul><li>Functional Verilog</li><li>Gate level</li></ul> |                                      |

| <ul> <li>Register transfer level</li> </ul>             |                                      |

| <ul><li>High-level behavioral</li></ul>                 |                                      |

|                                                         |                                      |

|                                                         |                                      |

|                                                         |                                      |

| SECURE, TRUSTED, AND ASSURED MICROEL                                                               | ACTRONICS                                                                                       | Arizona State University |  |  |

|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------|--|--|

| Continuous Assignments                                                                             |                                                                                                 |                          |  |  |

| <ul> <li>Continuous assignment statements assign one net to another or<br/>to a literal</li> </ul> |                                                                                                 |                          |  |  |

|                                                                                                    | Explicit continuous assignment wire [15:0] netA; wire [15:0] netB;                              |                          |  |  |

|                                                                                                    | <pre>assign netA = 16'h3333; assign netB = netA;</pre>                                          |                          |  |  |

|                                                                                                    | <pre>Implicit continuous assignment wire [15:0] netA = 16'h3333; wire [15:0] netB = netA;</pre> |                          |  |  |

|                                                                                                    |                                                                                                 |                          |  |  |

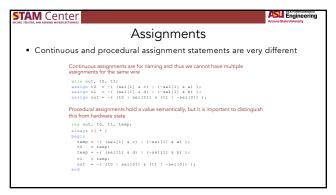

## Continuous Assignments Using continuous assignments to implement an RTL four input multiplexer module mux4 (input a, b, c, d input (input out); wire out, t0, t1; assign t0 = -( (sel[1] & c) | (-sel[1] & a) ); assign t1 = -( (sel[1] & d) | (-sel[1] & b) ); assign out = -( (t0 | sel[0]) & (t1 | -sel[0]) ); endmodule The order of these continuous assignment statements does not matter. They essentially happen in parallel!

```

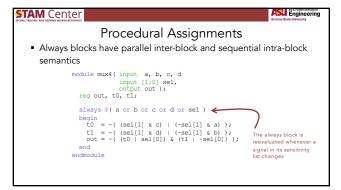

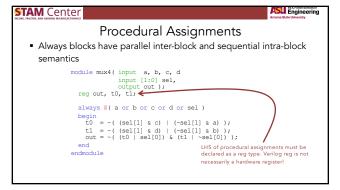

Procedural Assignments

Always blocks have parallel inter-block and sequential intra-block semantics

module mux4(input a, b, c, d input [1:0] sel, output out);

reg out, t0, t1;

always @( a or b or c or d or sel )

begin

t0 = ~((sel[1] & c) | (~sel[1] & a) );

t1 = ~((sel[1] & d) | (~sel[1] & b) );

out = ~((t0 | sel[0]) & (t1 | ~sel[0]) );

end

endinodule

The order of these procedural assignment statements does matter.

They essentially happen in sequentially!

```

## Procedural Assignments • Always blocks have parallel inter-block and sequential intra-block semantics module mux4( input a, b, c, d input [1:0] sel, output out ); reg out, t0, t1; always @( a or b or c or X or sel ) begin t0 = ~( (sel[1] & c) | (~sel[1] & a) ); t1 = ~( (sel[1] & d) | (~sel[1] & b) ); out = ~( (t0 | sel[0]) & (t1 | ~sel[0]) ); end endmodule What happens if we accidentally forget a signal on the sensitivity list?

29

# Procedural Assignments • Always blocks have parallel inter-block and sequential intra-block semantics module mux4 (input a, b, c, d input [1:0] sel, output out); reg out, t0, t1; always @(a or b or c or d or sel) begin t0 = -( (sel[1] & c) | (-sel[1] & a) ); t1 = -( (sel[1] & d) | (-sel[1] & b) ); out = -( (t0 | sel[0]) & (t1 | -sel[0]) ); end end endmodule Verilog-2001 provides special syntax to automatically create a sensitivity list for all signals read in the always block

## Always Blocks • Always blocks can contain more advanced control constructs \*\*module mux((input a, b, c, d input (input (input

32

```

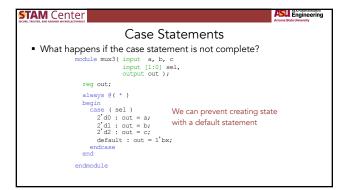

Case Statements

What happens if the case statement is not complete?

module mux3( input a, b, c input [1:0] sel, output out );

reg out;

always @( * )

begin

case ( sel )

2'd0 : out = a;

2'd1 : out = b;

2'd2 : out = c;

endcase

end

endmodule

```

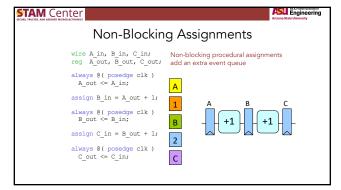

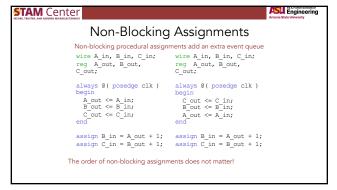

| STAM Center                                    |                                                                                                                                                            | ASI Engineering Arizona State University                     |  |  |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|--|

| Non-Blocking Assignments                       |                                                                                                                                                            |                                                              |  |  |

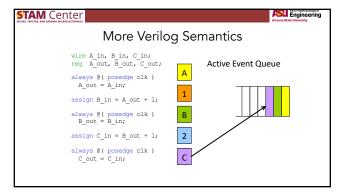

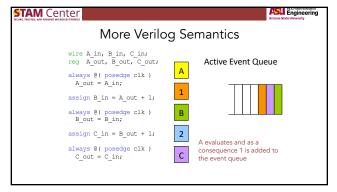

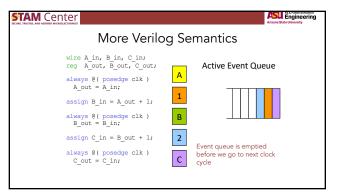

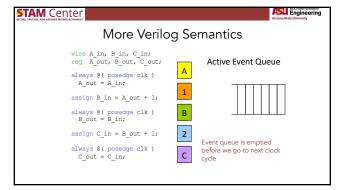

|                                                | A_in, B_in, C_in;<br>A_out, B_out, C_out;                                                                                                                  | Non-blocking procedural assignments add an extra event queue |  |  |

| A_C<br>assiç<br>alway<br>B_C<br>assiç<br>alway | <pre>ys @(posedge clk) put &lt;= A_in; gn B_in = A_out + 1; ys @(posedge clk) put &lt;= B_in; gn C_in = B_out + 1; ys @(posedge clk) put &lt;= C_in;</pre> | Active Event Queue  Non-Blocking Queue  C                    |  |  |

|                                                |                                                                                                                                                            |                                                              |  |  |

## **STAM** Center

### Blocking vs. Non-blocking

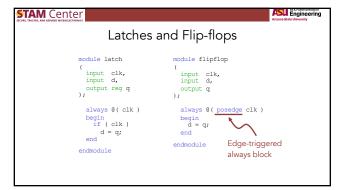

- Guidelines for using blocking and non-blocking assignment statements

- Flip-flops should use non-blocking

- Latches should use non-blocking

- Combinational logic should use blocking

- Do not mix combinational and sequential logic in the same always

- Do not assign to the same variable from more than one always block

49

ASU Engineering

ASU Engineering

### Behavioral Verilog Usage

- Behavioral Verilog is used to model the abstract function of a hardware module

- Characterized by heavy use of sequential blocking statements in large always blocks

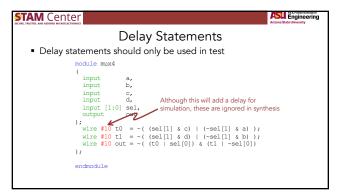

- Many constructs are not synthesizable but can be useful for behavioral

- Additional behavioral datatypes: integer, real

Magic initialization blocks: initial

- Magic delay statements:

50

**STAM** Center

High-level Behavior

• Verilog can be used to model the high-level behavior of a hardware block

```

System Testing

reg [10210] exe_filename;

initial begin

// This turns on VCD (plus) output

foredpluson(0);

// This gets is a program to load into memory from the command line

if readpluson(0);

// This gets is a program to load into memory from the command line

if readpluson(0);

// Stobe reset

foredpluson(0);

// Stobe r

```

## STAM Center SECURE, TRUSTED, AND ASSURED MICROELECTRONICS

ASU Engineering

## Take away points

- Structural Verilog enables us to describe a hardware schematic textually

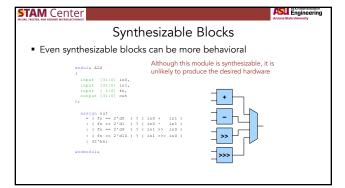

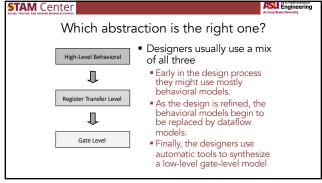

- Verilog can model hardware at three levels of abstraction

Gate level, register transfer level, and behavioral

- Understanding the Verilog execution semantics is critical for understanding blocking + non-blocking assignments

- Designers must have the hardware they are trying to create in mind when they write their Verilog