## CSE/CEN 598 Hardware Security & Trust

#### Trusted Digital System Design: Verilog Fundamentals II

Prof. Michel A. Kinsy & Mishel Paul

## Computer System Description

- A system is a set of related components that works as a whole to achieve a goal.

- A system contains:

- Inputs

- Behavior

- Outputs

Behavior is a function that translates inputs to outputs

# Verilog Fundamentals

- Data types

- Structural Verilog

- Functional Verilog

- Gate level

- Register transfer level

- High-level behavioral

## Verilog Test Bench Basics

- Test Bench A wrapper module to apply test inputs to a "Device Under Test"

- Also written in Verilog

- Three main components

- Device Under Test Instantiation

- Test Inputs

- Output Checking

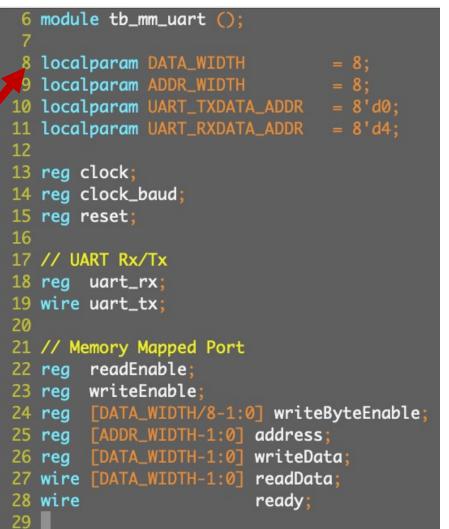

- Declare test bench module

- No inputs/output

6 module tb\_mm\_uart (); 8 localparam DATA\_WIDTH 9 localparam ADDR\_WIDTH 10 localparam UART\_TXDATA\_ADDR 11 localparam UART\_RXDATA\_ADDR = 8' d4:12 13 reg clock; 14 reg clock\_baud; 15 reg reset; 16 17 // UART Rx/Tx 18 reg uart\_rx; 19 wire uart\_tx; 20 21 // Memory Mapped Port 22 reg readEnable; 23 reg writeEnable 24 reg [DATA\_WIDTH/8-1:0] writeByteEnable; 25 reg [ADDR\_WIDTH-1:0] address; [DATA\_WIDTH-1:0] writeData; 26 rea 27 wire [DATA\_WIDTH-1:0] readData; 28 wire ready: 29

- Declare test bench module

- No inputs/output

- Declare parameters for module/DUT

- Declare test bench module

- No inputs/output

- Declare parameters for module/DUT

- Declare test inputs/outputs

- "reg" means input for a test bench

- "wire" means output for a test bench

|    | <pre>module tb_mm_uart ();</pre> |                  |

|----|----------------------------------|------------------|

| 7  |                                  |                  |

| 8  | localparam DATA_WIDTH            | = 8;             |

| 9  | localparam ADDR_WIDTH            | = 8;             |

| 10 | localparam UART_TXDATA           | $\_ADDR = 8'd0;$ |

| 11 | localparam UART_RXDATA           | $\_ADDR = 8'd4;$ |

| 12 |                                  |                  |

| 13 | reg clock;                       |                  |

|    | reg clock_baud;                  |                  |

|    | reg reset;                       |                  |

| 16 | ,                                |                  |

|    | // UART Rx/Tx                    |                  |

|    | reg uart_rx;                     |                  |

|    | wire uart_tx;                    |                  |

| 20 |                                  |                  |

|    | // Memory Mapped Port            |                  |

|    |                                  |                  |

|    | <pre>reg readEnable;</pre>       |                  |

|    | reg writeEnable;                 |                  |

|    | reg [DATA_WIDTH/8-1:0]           |                  |

|    | reg [ADDR_WIDTH-1:0] (           |                  |

|    | reg [DATA_WIDTH-1:0] N           |                  |

|    | wire [DATA_WIDTH-1:0]            |                  |

|    | wire                             | ready;           |

| 29 |                                  |                  |

- Declare test bench module

- No inputs/output

- Declare parameters for module/DUT

- Declare test inputs/outputs

- "reg" means input for a test bench

- "wire" means output for a test bench

- Some reg/wires are more than 1 bit

- readData is DATA\_BITS large

| _ |            |                                                    |

|---|------------|----------------------------------------------------|

|   |            | nodule tb_mm_uart ();                              |

|   | 7          |                                                    |

|   | 8          | .ocalparam DATA_WIDTH = 8;                         |

|   | 9          | .ocalparam ADDR_WIDTH = 8;                         |

| 1 | LØ         | .ocalparam UART_TXDATA_ADDR = 8'd0;                |

| 1 | 1          | .ocalparam UART_RXDATA_ADDR = 8'd4;                |

| 1 | 12         |                                                    |

| 1 | 13         | reg clock;                                         |

| 1 | 4          | eg clock_baud;                                     |

| 1 | 15         | reg reset;                                         |

| 1 | 16         |                                                    |

| 1 | 17         | // UART Rx/Tx                                      |

| 1 | L <b>8</b> | eg uart_rx;                                        |

|   |            | vire uart_tx;                                      |

|   | 20         |                                                    |

| 2 | 21         | // Memory Mapped Port                              |

|   |            | eg readEnable;                                     |

|   |            | eg writeEnable;                                    |

|   |            | <pre>reg [DATA_WIDTH/8-1:0] writeByteEnable;</pre> |

|   |            | eg [ADDR_WIDTH-1:0] address;                       |

|   |            | eg [DATA_WIDTH-1:0] writeData;                     |

|   |            | vire [DATA_WIDTH-1:0] readData;                    |

|   |            | vire ready;                                        |

|   | 29         |                                                    |

|   |            |                                                    |

Instantiate Device Under Test

| 44 | mm_uart DUT ( |                       |

|----|---------------|-----------------------|

|    | .clock        | (clock),              |

| 46 | .reset        | (reset),              |

| 47 | .uart_rx      | (uart_rx),            |

| 48 | .uart_tx      | (uart_tx),            |

| 49 | // Memory Map | ped Port              |

| 50 | .readEnable   | (readEnable),         |

| 51 | .writeEnable  | (writeEnable),        |

| 52 | .writeByteEna | ble(writeByteEnable), |

| 53 | address       | (address),            |

| 54 | .writeData    | (writeData),          |

| 55 | .readData     | (readData),           |

| 56 | . ready       | (ready)               |

| 57 | )             |                       |

- Instantiate Device Under Test

- Connect DUT inputs/outputs to test bench signals

- DUT I/O after "."

- Test bench signals inside parenthesis

- Names are frequently identical

| 44 r | mm_uart DUT (  |                      |

|------|----------------|----------------------|

| 45   | .clock         | (clock),             |

| 46   | .reset         | (reset),             |

| 47   | .uart_rx       | (uart_rx),           |

| 48   | .uart_tx       | (uart_tx),           |

| 49   | // Memory Mapp | ed Port              |

| 50   | .readEnable    | (readEnable),        |

| 51   | .writeEnable   | (writeEnable),       |

| 52   | uniteByteEnab  | le(writeByteEnable), |

| 53   | .address       | (address),           |

| 54   | .writeData     | (writeData),         |

| 55   | .readData      | (readData),          |

| 56   | . ready        | (ready)              |

| 57   |                |                      |

- Test Stimulus

- Apply inputs at given times of simulation

| 138 | //                                   |

|-----|--------------------------------------|

| 139 | //                                   |

| 140 | // Simulation                        |

| 141 | 11                                   |

| 142 | //                                   |

| 143 |                                      |

| 144 | //100MHz CLK                         |

| 145 | always #5 clock = ~clock;            |

|     | always #50 clock_baud = ~clock_baud; |

| 147 |                                      |

| 148 | initial begin                        |

| 149 | initialize;                          |

| 150 | inactive(100);                       |

| 151 | <pre>test_init;</pre>                |

| 152 | inactive(100);                       |

| 153 | test_tx;                             |

| 154 | inactive(100);                       |

| 155 | test_rx;                             |

| 156 | inactive(100);                       |

| 157 | <pre>test_exit;</pre>                |

| 158 | end                                  |

- Test Stimulus

- Apply inputs at given times of simulation

- Clock Setup

- Toggle "clock" signal every 5 simulation timesteps

- "Always" block repeats in a loop

| 138<br>139 | //                                              |

|------------|-------------------------------------------------|

|            |                                                 |

|            | // Simulation                                   |

| 141        |                                                 |

| 142        | //                                              |

| 143        |                                                 |

| 144        | //100MHz CLK                                    |

| 115        | always #5 clock = ~clock;                       |

| 146        | <pre>always #50 clock_baud = ~clock_baud;</pre> |

| 147        | · - · ·                                         |

| 148        | initial begin                                   |

| 149        | initialize;                                     |

| 150        | <pre>inactive(100);</pre>                       |

| 151        | <pre>test_init;</pre>                           |

| 152        | inactive(100);                                  |

| 153        | test_tx;                                        |

| 154        | <pre>inactive(100);</pre>                       |

| 155        | test_rx;                                        |

| 156        | inactive(100);                                  |

| 157        | <pre>test_exit;</pre>                           |

| 158        | end                                             |

- DUT test inputs

- "Initial" Block Apply test inputs once

| 138 | //                                   |

|-----|--------------------------------------|

| 139 | 11                                   |

| 140 | // Simulation                        |

| 141 | 11                                   |

| 142 | //                                   |

| 143 |                                      |

| 144 | //100MHz CLK                         |

| 145 | always #5 clock = ~clock;            |

| 146 | always #50 clock_baud = ~clock_baud; |

| 147 |                                      |

| 140 | initial begin                        |

|     | initialize;                          |

|     | inactive(100);                       |

|     | test_init;                           |

|     | inactive(100);                       |

|     | test_tx;                             |

|     | inactive(100);                       |

|     | test_rx;                             |

|     | inactive(100);                       |

| 157 |                                      |

| 158 | end                                  |

|     |                                      |

- DUT test inputs

- "Initial" Block Apply test inputs once

- Use "Tasks" to apply specific test inputs

- Initialize, inactive, test\_tx, test\_rx, and test\_exit are tasks

- A task groups a set of inputs for re-use

| 138 //                                   |

|------------------------------------------|

| 139 //                                   |

| 140 // Simulation                        |

| 141 //                                   |

| 142 //                                   |

| 143                                      |

| 144 //100MHz CLK                         |

| 145 always #5 clock = ~clock;            |

| 146 always #50 clock_baud = ~clock_baud; |

| 147                                      |

| 148 initial begin                        |

| 149 initialize;                          |

| 150 inactive(100);                       |

| <pre>151 test_init;</pre>                |

| <pre>152 inactive(100);</pre>            |

| 153 test_tx;                             |

| 154 inactive(100);                       |

| 155 test_rx;                             |

| 156 inactive(100);                       |

| <pre>157 test_exit;</pre>                |

| 158 end                                  |

- Initialize task

- \$display writes to console

| 67 | task initialize;                         |

|----|------------------------------------------|

| 68 | begin                                    |

|    | <pre>\$display("INITIALIZING");</pre>    |

| 70 |                                          |

| 71 | clock_baud =1'b1;                        |

| 72 |                                          |

| 73 |                                          |

| 74 |                                          |

| 75 |                                          |

| 76 | writeByteEnable = 4'h0;                  |

| 77 |                                          |

| 78 |                                          |

| 79 |                                          |

| 80 | <pre>repeat (3) @ (posedge clock);</pre> |

| 81 | reset = $1'b0;$                          |

| 82 | end                                      |

| 83 | endtask                                  |

- Initialize task

- \$display writes to console

- Set inputs to specific values

- All set at the same simulation time

| 67 | task initialize;         |                          |

|----|--------------------------|--------------------------|

| 68 | begin                    |                          |

| 69 |                          | LIZING");                |

| 70 | <pre>clock = 1'b1;</pre> |                          |

| 71 | clock_baud =1'b1         |                          |

| 72 | uart_rx = 1'b1;          |                          |

| 73 | reset = 1'b1;            |                          |

| 74 | readEnable               | = 1'b0;                  |

| 75 | writeEnable              | = 1'b0;                  |

| 76 | writeByteEnable          | = 4'h0;                  |

| 77 | address                  | = 32'h0;                 |

| 78 | writeData                | = 32'h0;                 |

| 79 |                          |                          |

| 80 | repeat (3) @ (po         | <pre>sedge clock);</pre> |

| 81 | reset = 1'b0;            |                          |

|    | end _                    |                          |

| 83 | endtask                  |                          |

- Initialize task

- \$display writes to console

- Set inputs to specific values

- All set at the same simulation time

- Repeat statement waits for 3 clock cycles

- Reset signal stays high for 3 clock cycles

| 67       | teck initialized                      |

|----------|---------------------------------------|

|          | task initialize;                      |

| 68       | begin                                 |

| 69       | <pre>\$display("INITIALIZING");</pre> |

| 70       | <pre>clock = 1'b1;</pre>              |

| 71       | clock_baud =1'b1;                     |

| 72       | uart_rx = 1'b1;                       |

| 73       | reset = 1'b1;                         |

| 74       | <pre>readEnable = 1'b0;</pre>         |

| 75       | writeEnable = 1'b0;                   |

| 76       | writeByteEnable = 4'h0;               |

| 77       | address = 32'h0;                      |

| 78       | writeData = 32'h0;                    |

| 73<br>80 |                                       |

| 80       | repeat (3) @ (posedge clock);         |

| 81       | reset = $1'b0;$                       |

| 82       | end                                   |

| 83       | endtask                               |

- Initialize task

- \$display writes to console

- Set inputs to specific values

- All set at the same simulation time

- Repeat statement waits for 3 clock cycles

- Reset signal stays high for 3 clock cycles

- Apply new inputs after waiting

- Reset signal lowered

| ~ - |                                          |

|-----|------------------------------------------|

| 67  | task initialize;                         |

| 68  | begin                                    |

| 69  | <pre>\$display("INITIALIZING");</pre>    |

| 70  | <pre>clock = 1'b1;</pre>                 |

| 71  | clock_baud =1'b1;                        |

| 72  | uart_rx = 1'b1;                          |

| 73  | reset = 1'b1;                            |

| 74  | <pre>readEnable = 1'b0;</pre>            |

| 75  | writeEnable = 1'b0;                      |

| 76  | writeByteEnable = 4'h0;                  |

| 77  | address = 32'h0;                         |

| 78  | writeData = 32'h0;                       |

| 79  |                                          |

| 80  | <pre>repeat (3) @ (posedge clock);</pre> |

| δı  | reset = 1'b0;                            |

| 82  | end                                      |

| 83  | endtask                                  |

### Additional Resources

- Asic-world.com

- Verilog Tutorial "Art of Writing Test Benches"

- Additional info on Verilog syntax

- Getting started examples

- yosyshq.net/yosys/

- Documentation for open-source synthesis tool

- Used in Project 3

#### **Obfuscated Netlists**

- Verilog Obfuscated with Yosys

- Read in Verilog

- Parse to internal representation

- Write out to plain Verilog again

- Obfuscation

- Parsed Verilog is already hard to read/understand

- Renamed wires, regs, and modules

- Top-level ports still the same

| 648 | <pre>assign _19_ = _48_(8'h00, { _29_[7:0],</pre> |

|-----|---------------------------------------------------|

| 649 | assign _22_ = _23_ ? _19_ : 8'h00;                |

| 650 | assign _24_ = _25_ ? 8'h00 : _22_;                |

| 651 | assign _26_ = _27_ ? 8'h00 : _24_;                |

| 652 | assign _28_ =  TX89tb;                            |

| 653 | UXmg CJTDIIx 🕻                                    |

| 654 | .ET5uS(pRm6∨GPowaWGO),                            |

| 655 | .Jm∨(m6Pow∨),                                     |

| 656 | .Kogc(1'h0),                                      |

| 657 | .X8qqE(GooRagLjgP4dw),                            |

| 658 | .ffkGpLq4E(MKHJ∨93PQOdt0rllG),                    |

| 659 | .jT1j(TX89tb),                                    |

| 660 | .k7ZJ(UMIaxeJUmGYR),                              |

| 661 | .kfno(ewTNYHIdEpVj0),                             |

| 662 | .sMrlR(NXKSJycPvnP0a),                            |

| 663 | vgGEfgslfn(Zl6sD57Nd43NzyGl9f)                    |

| 664 | );                                                |

| 665 |                                                   |

### Take away points

- Structural Verilog enables us to describe a hardware schematic textually

- Verilog can model hardware at three levels of abstraction

- Gate level, register transfer level, and behavioral

- Understanding the Verilog execution semantics is critical for understanding blocking + non-blocking assignments

- Designers must have the hardware they are trying to create in mind when they write their Verilog