Computer System Description • A system is a set of related components that works as a whole to achieve a goal. • A system contains: • Inputs • Behavior • Outputs • Behavior is a function that translates inputs to outputs 2

| STAM Center                                                                                                                    | Arizona State University                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

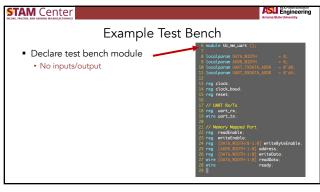

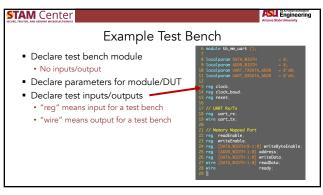

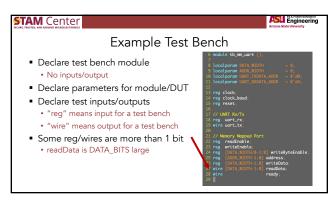

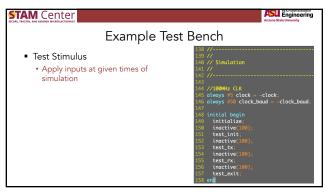

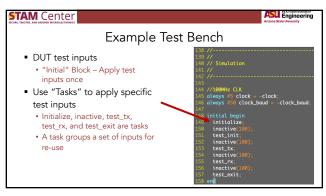

| Example Test                                                                                                                   | t Bench                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <ul> <li>Declare test bench module <ul> <li>No inputs/output</li> </ul> </li> <li>Declare parameters for module/DUT</li> </ul> | 6 module telementarit (c);<br>7 localparam MAR_MIDH - 6;<br>10 collaparam MAR_MIDH - 6;<br>11 localparam MAR_MIDH - 6;<br>12 localparam MAR_MIDH - 6;<br>13 reg Clock Load<br>13 reg Clock Load<br>14 reg Clock Load<br>15 reg reset;<br>17 // Manoy Magaed Port<br>12 reg enditable [<br>12 reg enditable [<br>12 reg enditable [<br>12 reg enditable [<br>13 reg full collaps;<br>14 // Menoy Magaed Port<br>12 reg enditable [<br>13 reg full collaps;<br>14 // Menoy Magaed Port<br>12 reg enditable [<br>13 reg full collaps;<br>14 // Manoy Magaed Port<br>12 reg enditable [<br>13 reg full collaps;<br>14 // Manoy Magaed Port<br>15 reg (CMT_MITH=10) articlebts<br>15 reg (CMT_MITH=10) artic |

| _ |

|---|

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|                                                   | Arizona State University                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

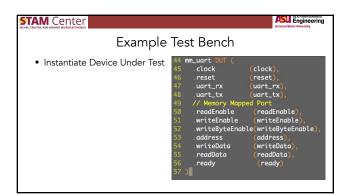

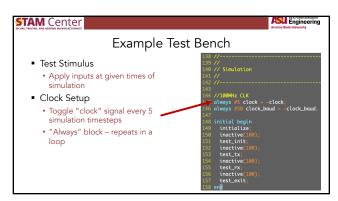

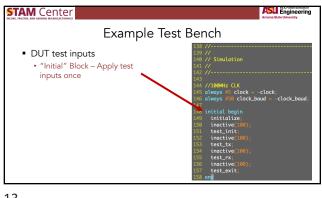

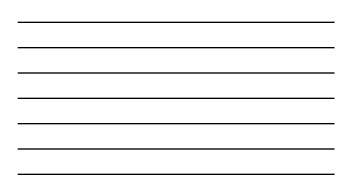

| Example Test Bench                                |                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

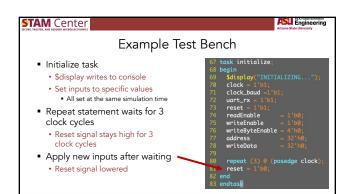

| Initialize task     * \$display writes to console | <pre>67 task initialize;<br/>68 begin<br/>5 Sdispley("INITIALIZING");<br/>70 clock = 1'b1;<br/>71 clock_baud =1'b1;<br/>72 uart_rx = 1'b1;<br/>73 reset = 1'b1;<br/>74 readEnable = 1'b8;<br/>75 writeEnable = 4'h0;<br/>76 writeEnable = 4'h0;<br/>77 address = 32'h0;<br/>78 reset = 32'h0;<br/>79 reset = 1'b0;<br/>80 reset = 1'b0;<br/>81 enable = 1'b0;<br/>82 end<br/>83 endtast</pre> |  |  |  |

|                                                                                                                                                                          | Arizona State University                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

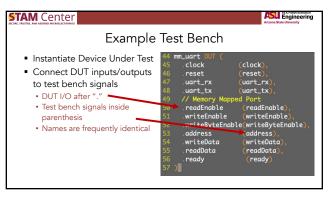

| Example Te                                                                                                                                                               | est Bench                                                                                                                                                                                                                                                                                                                                        |

| <ul> <li>Initialize task</li> <li>\$display writes to console</li> <li>Set inputs to specific values <ul> <li>All set at the same simulation time</li> </ul> </li> </ul> | 67 task initialize;<br>68 begin<br>69 \$display("INITIALIZING");<br>71 clock_bad =1'b1;<br>72 uart_rx = 1'b1;<br>73 reast = 1'b1;<br>74 readEnable = 1'b8;<br>75 writeEnable = 1'b8;<br>76 writeEnable = 4'h8;<br>77 address = 32'h8;<br>78 writeEnable = 32'h8;<br>79 repeat (3) @ (posedge clock);<br>81 reset = 1'b0;<br>82 end<br>83 endtask |

| <br> |

|------|

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

| _    |

## **STAM** Center ASU Engineering Additional Resources Asic-world.com • Verilog Tutorial – "Art of Writing Test Benches" • Additional info on Verilog syntax • Getting started examples yosyshq.net/yosys/ • Documentation for open-source synthesis tool • Used in Project 3

19

20

## **STAM** Center

ASU Engineering

## Take away points

- Structural Verilog enables us to describe a hardware schematic textually

- Verilog can model hardware at three levels of abstraction • Gate level, register transfer level, and behavioral

- Understanding the Verilog execution semantics is critical for

- understanding blocking + non-blocking assignments Designers must have the hardware they are trying to create in mind when they write their Verilog