Zeno Architecture: A Secure High-Performance Computing RISC-V Processor Architecture Design

Lead Students: Alan Ehret and Donato Kava

High-performance computing (HPC) and supercomputing systems are used to tackle the most challenging computational problems in medicine, defense, weather, chemistry, engineering, oil and gas explorations, and more. Especially, when it comes to big data analytics and artificial intelligence computing in these applications.

The traditional evolution of the HPC field has create an ecosystem in which oftentimes a small number of systems is commissioned by a government agency through a computer system vendor using (i) proprietary intellectual property (IP) blocks and (ii) obscure or highly under-specified system architecture. These systems are held in the domain of top-tier research universities, national laboratories and large organizations. Consequently, the broader HPC community is compelled to narrow their algorithm optimization and software development efforts to these architectures.

One can argue that the lack of open-architecture concepts in HPC and server-class systems has severely hindered innovation and progress in the field. This scarcity limits hardware-level design space exploration, and as a result, algorithmic optimization and software innovations are also constrained. System-level security-related research efforts are generally abandoned due to the lack of visibility or access to micro-architecture details to test, analyze or validate vulnerabilities, threats or risks.

With the introduction of the RISC-V instruction set architecture (ISA) and its rapidly growing ecosystem and community, there may be an opportunity to open up the HPC and server-class systems design space. The RISC-V being an open, royalty-free, ISA with many extension specifications, it offers a high degree of customization. The ability to add extensions to the base ISA is an attractive option for high performance applications with different configurations and security constraints.

In this spirit, we aim under this research effort to develop a specification for a server-class RISC-V processor. Existing architectures and ISAs are proprietary and expensive/difficult to customize. In contrast, the RISC-V ISA is open-source. Although, early adopters have targeted lower-end embedded/IoTs (Internet of Things) and consumer devices, it has the potential, given its ecosystem and adoption trajectory, to become the base of an open-source server architecture, where high preference and security are both first class system characteristics.

Generally, there are three classes of server of interest which share common goals but may have different configuration profiles and extensions: (1) datacenter analytic (HTC) server, (2) cloud virtualization server, and (3) HPC compute server.

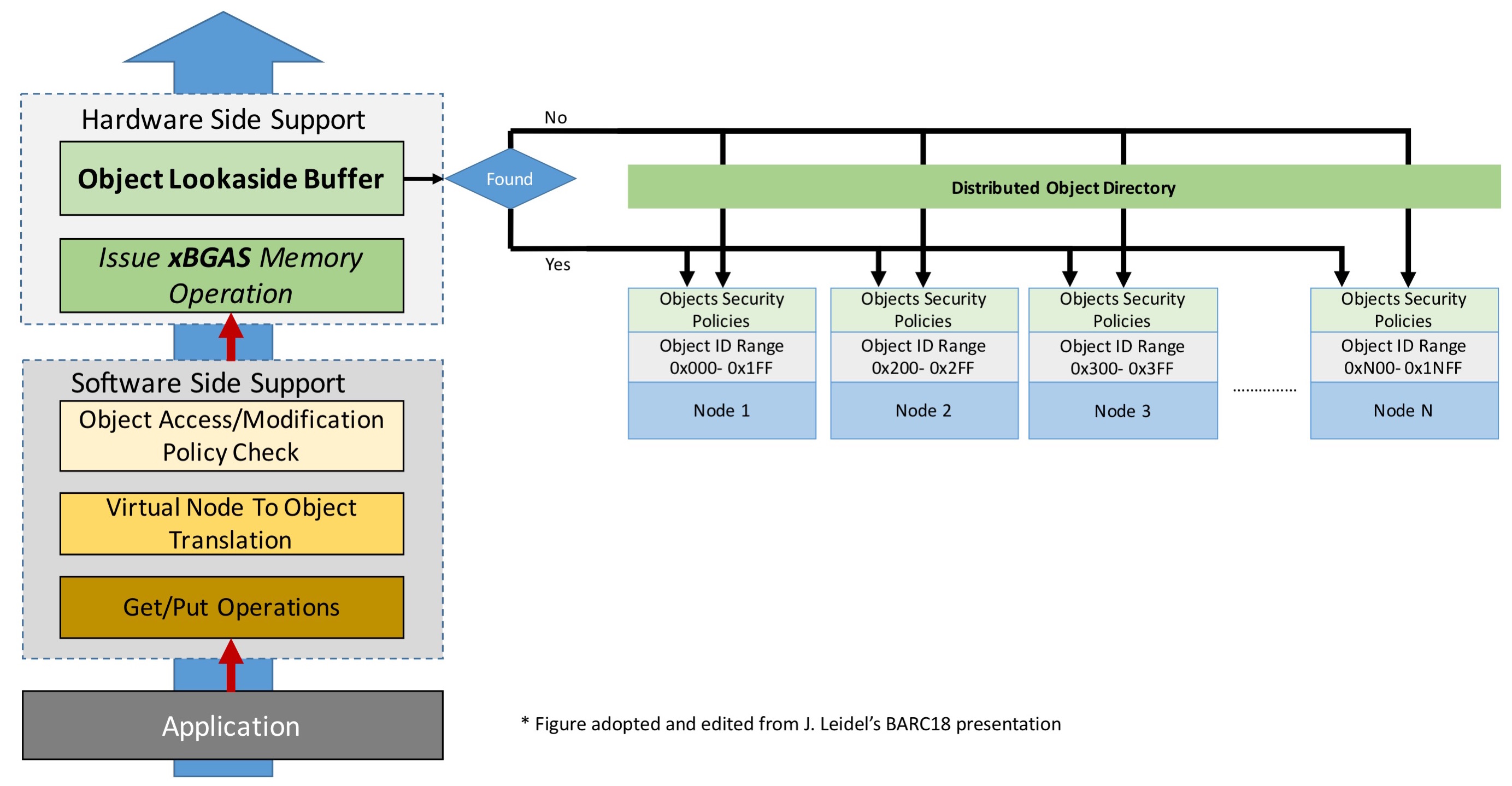

To leverage existing efforts around the RISC-V ISA, we will start with the xBGAS (Extended Base Global Address Space) architecture. Recognizing the problems associated with the conventional message passing approach in data centers, clouds and other HPC, John Leidel et al., created the xBGAS RISC-V architecture to provide extended addressing capabilities. The framework can support multiple target application spaces and system architectures.